Tales from the Cube: Coffee-break mistake Pg 62

Engineering the next generation Pg 10

> Semiconductors develop an EUV ecosystem Pg 24

Design Ideas Pg 49

Supply Chain Pg 58

1

-

0

Blind

De

۲

**Sleep** Time

PAT

• Issue 17/2011 www.edn.com

R

#### -----0 0 0 ,0 (a E 13

VOICE OF THE ENGINEER

Page 34

CHIP-AND-PACKAGE CO-DESIGN RELIEVES PRESSURE ON COMPLEX DESIGNS Page 27

> 2011 EEERR PR DST

Digi-Key

### The Next Generation of Signal Integrity Testing

### Can you see what dangers are lurking in your multi-lane design?

You already know your scope is inadequate for detecting low-probability events, but did you know that a single-channel BER tester isn't enough to find errors caused by crosstalk?

#### How are you testing crosstalk susceptibility?

Our parallel channel BERT provides multiple aggressors with a phase Delay Sweep feature that independently sweeps the aggressor's transitions over one, two, or four UI. Each aggressor is swept at a different rate. This creates the perfect storm – the guaranteed worst-case timing conditions that ensure you are thoroughly testing your DUT's susceptibility to crosstalk.

#### Don't risk missing a design flaw. Load all channels. Sweep your aggressors.

#### Ideal For:

- CFP

- QSFP

- CXP

- Active Optical Cables

Scan the QR code or visit goo.gl/P6dNy to see a product video The most compact solution available

#### Affordability without compromise

see for yourself: www.centellax.com/next\_gen

## RATED #1 On-Time Delivery

Rated number one, Distributor Reputation - "Provides on-time delivery" by North American electronic engineers in the UBM/EE Times 2011 Distributor Customer Preference Study (June 2011). Digi-Key is an authorized distributor for all supplier partners. New products added daily. © 2011 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

### Find It Here, Faster.

The Newest Products for Your Newest Designs®

er and Mouser Electronics are registered trademarks of Mouser Electronics, Inc

Authorized distributor for the most advanced semiconductors and electronic components. Get What's Next. Right now at mouser.com.

a tti company

Blind

TAC

Nfm

### **EDN** contents

#### Chip-and-package co-design relieves pressure on complex designs

27 Co-design accomplishes more with less by performing more design tasks in a shorter design cycle. by Darvin Edwards, Texas Instruments

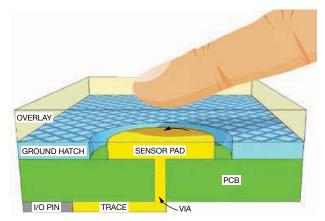

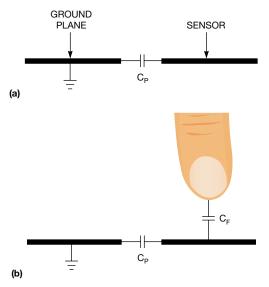

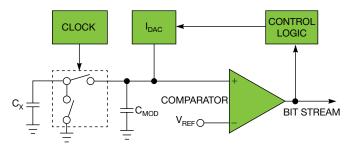

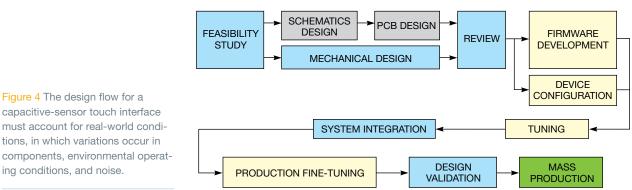

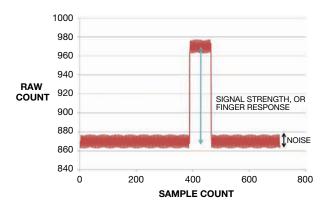

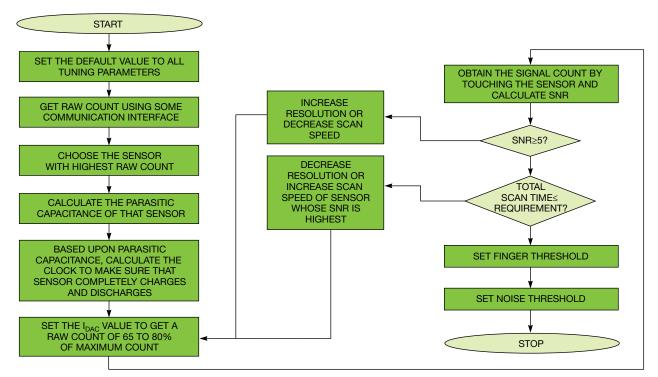

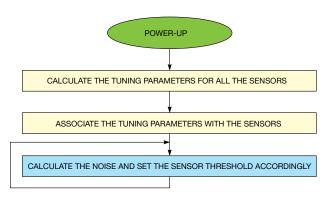

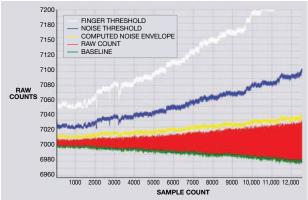

### Designing reliable capacitive touch interfaces

43 Understand how to enhance the hardware and software reliability of this increasingly popular user interface for appliances and instruments. *by Sachin Gupta, Prakhar Goyal,*

by Sachin Gupta, Prakhar Goyal, and Kurian Polachan, Cypress Semiconductor Corp

DSOs: The banner specs tell only part of the story

34 To make an intelligent choice of a scope, you must know its banner specs – bandwidth, sampling rate, and memory depth. Before you sign a purchase order, though, you'd be wise to find out much more. *by Dan Strassberg, Contributing Technical Editor*

COVER: DAVID NICASTRO/PENCIL IMAGE: ISTOCKPHOTO.COM

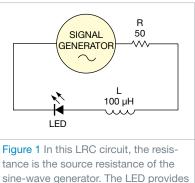

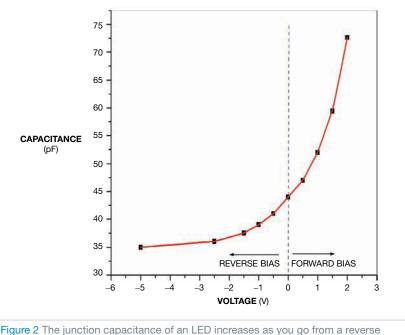

### DESIGNIDEAS

49 Polynomial rotation accelerates CRC calculations

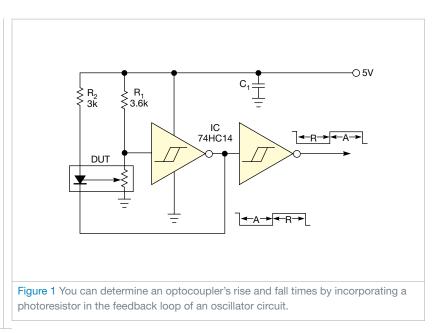

50 Simple circuit measures optocoupler's response time

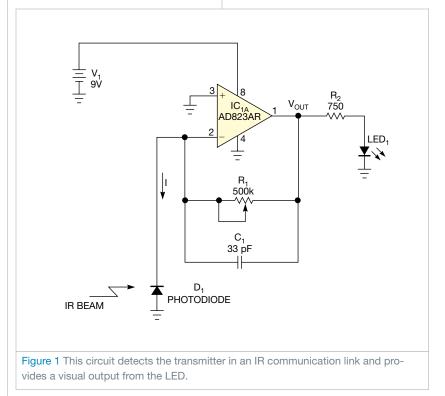

52 Circuit provides visual verification of IR pulses

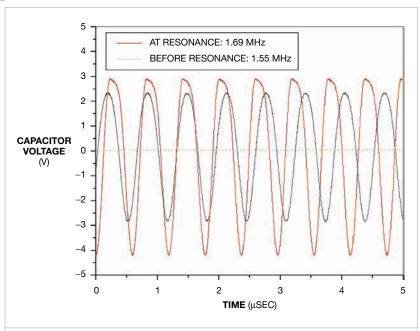

54 An LED's intrinsic capacitance works in a 650-mV LRC circuit

Send your Design Ideas to edndesignideas@ubm.com.

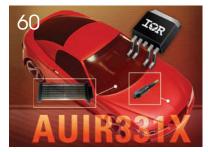

### **Delivering Real Power**

#### Compact, Powerful CCM PFC from 75W to 4kW+

| PFC Control ICs |                                                                                             |  |  |  |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Part Number     | Description                                                                                 |  |  |  |  |  |  |  |  |

| IR1152          | Fixed 66KHz switching frequency with brownout protection and dual OVP protection            |  |  |  |  |  |  |  |  |

| IR1153          | Fixed 22KHz switching frequency with brownout protection<br>and programmable OVP protection |  |  |  |  |  |  |  |  |

| IR1155          | Programmable switching frequency and programmable OVP protection                            |  |  |  |  |  |  |  |  |

#### 600 V PFC IGBTs for High Power Systems I\_@ 100C V\_CE(on) (max) Circuit Part Number Package (V) (A) IRGB20B60PD1 22 2.35 TO-220AB IRGP20B60PD 22 2.35 TO-247AC Co-Pack IRGP35B60PD 35 2.15 TO-247AC IRGP50B60PD1 2.35 TO-247AC 45 IRG4(B/IB)C20W 6.5 2.6 TO-220AB; TO-220 FullPak IRG4(B/IB/P)C30W 12 2.7 TO-220AB; TO-220 FullPak; TO-247AC IRG4(B/P)C40W 20 2.5 TO-262; TO-220AB; TO-247AC

2.3

1.85

2.14

2.1

IRG4PC50W

IRGP4069

IRGP4063

IRGP4066

Discrete

27

35

48

90

# The µPFC family of controller ICs radically alters traditional thinking about PFC solutions. The IR115x uses a "One-Cycle Control integrator with reset" technique to deliver the high performance of Continuous Conduction Mode (CCM) PFC with the simplicity and low component count of Discontinuous Current Mode (DCM).

#### Features

- Small, easy, powerful solution

- Fast time to market

- Enables compliance with energy standards (1W, Blue Angel, Energy Star)

- No AC line voltage sense required

- 0.999 power factor

- Switching frequency of 22kHz, 66kHz or programmable value available

- Average current mode control

- Cycle by cycle peak current limit system protection

### International

for more information call 1.800.981.8699 or visit us at www.irf.com

TO-247AC

TO-247AC

TO-247AC

#### contents 9.8.11

- 15 Scope, spectrum-analyzer combination provides time-correlated signals

- 16 Orca shows a full dual-mode Bluetooth core in CMOS

- 18 Synchronous, forwardconverter chip set provides active clamp, deters transformer saturation

- 18 True-green laser module targets use in smartphone picoprojectors

- 20 Bridgelux plans to bring economies of GaN-on-Si to HB LEDs in 24 months

- 20 Watch out for well-madebut counterfeit-chips

- 22 New architecture promises better battery

- 22 Source code for µC/OS-III is now available

#### **DEPARTMENTS & COLUMNS**

- EDN online: Join the conversation; Content; Engineering Community

- 10 EDN.comment: Engineering the next generation

- 24 Inside Nanotechnology: Semiconductors develop an EUV ecosystem

- 58 **Supply Chain:** Tool is in the works to standardize conflict-minerals tracking; Indian semiconductor consumption to grow 15.5%

- 60 Product Roundup: Switches and relays; Enclosures

- 62 Tales from the Cube: Coffee-break mistake

EDN® (ISSN# 0012-7515) is published semimonthly by UBM Electronics, 600 Community Drive, Manhasset, NY 11030-3825. Periodicals postage paid at Manhasset, NY, and at additional mailing offices. SUBSCRIPTIONS-Free to qualified subscribers as defined on the subscription card. Rates for nonqualified subscriptions, including all issues: US, \$150 one year; \$250 two years; \$300 three years. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. For telephone inquiries regarding subscriptions, call 847-559-7597. E-mail: edn@orneda.com. CHANGE OF ADDRESS - Notices should be sent promptly to PO Box 47461, Plymouth, MN 55447. Please provide old mailing label as well as new address. Allow two months for change. NOTICE-Every precaution is taken to ensure accuracy of content; however, the publishers cannot accept responsibility for the correctness of the information supplied or advertised or for any opinion expressed herein. POSTMASTER—Send address changes to EDN, PO Box 47461, Plymouth, MN 55447. CANADA POST: Publications Mail Agreement 40612608. Return undeliverable Canadian addresses to BleuChip International, PO Box 25542, London, ON N6C 6B2. Copyright 2011 by United Business Media. All rights reserved. Reproduction in whole or part without written permission is prohibited. Volume 56, Number 17 (Printed in USA)

#### INNOVATORS CREATE INTELLIGENT ROBOTS THAT TRANSFORM MANUFACTURING.

KUKA Robots Building the Future BMW 1 Series Regensburg, Germany

When the innovators at KUKA decided to create the foundation for the automation of tomorrow, they decided to work with Wind River. Building upon the proven reliability and breakthrough performance of our VxWorks and multi-core platforms, the KUKA team developed their revolutionary KR C4 controller—a safer, more powerful, more flexible system that allows all integrated controllers to share a common database and infrastructure. And by working with Wind River, they did it all ahead of schedule, under budget, and with far less risk.

Please visit http://www.windriver.com/customers to learn more about how Wind River customers have transformed their devices.

WIND RIVER INNOVATORS START HERE.

d by KUKA

#### JOIN THE CONVERSATION

Comments, thoughts, and opinions shared by EDN's community

### In response to Paul Rako's Prying Eyes tear-down, "The Tektronix 1101 oscilloscope-probe power supply," at http://bit.ly/noHonC, David Lockman commented:

"To paraphrase Santayana, those who cannot learn from history are doomed to repeat it. This is an opportunity to learn how to solve design problems, and perhaps save yourself a little time and effort when you are called upon to solve a similar problem."

In response to "iFixit tears down a smart meter to evaluate electro-smog," posted in Margery Conner's PowerSource blog at http://bit.ly/EDN\_ElectroSmog, Davidiode commented:

"I love this stuff. These tear-downs are fascinating. Now and historically, the scientific/technical have always been held hostage by myths and fuzzy thinking, worried about what they don't understand. The Al Gores of the world always get more traction than the Bob Peases."

#### In response to "Front-end, back-end, and the places in between," posted in Ron Wilson's Practical Chip Design blog at http://bit.ly/EDN\_FrontBack, William Ketel commented:

"Ron certainly makes an accurate assessment of the problem. I offer here a suggestion which many will scream at as heresy, since it would reduce the options for "product differentiation," and all the marketing wonks will throw up. But how about holding the hardware constant and just changing the software? One large designed die, and more creative code? Saving a few million on a new hardware spin should be an option worth something, especially if the production yields are already high and stable. Just a suggestion."

EDN invites all of its readers to constructively and creatively comment on our content. You'll find the opportunity to do so at the bottom of each article and blog post. To review current comment threads on EDN.com visit this page: http://bit.ly/EDN\_Talkback.

#### **ENGINEERING COMMUNITY**

Opportunities to get involved and show your smarts

In EDN's Tales From The Cube, engineers relate their most vexing design challenges—and how they conquered them. What's your Tale? Tell us about a memorable experience you've had successfully solving an engineering problem at work or in your spare time, and you could win a Tektronix scope! Visit this page for contest information: http://bit.ly/Tales\_EDN.

#### WHEN KIDS REALLY HAD FUN WITH SCIENCE

Were you a kid who almost blew up the garage or nearly burned down the house on your way to becoming an engineer? *EDN*'s Paul Rako wonders if today's supersafe, momapproved science and tech toys for kids hinder learning by taking the fun out of experimenting. He and Analog Devices fellow Barrie Gilbert also share some of their dangerous but fun experiments from childhood in this blog post. Check it out and share your own memories in the post's comment field.

#### http://bit.ly/nEVdvl

[www.edn.com]

from the

EDN.COMMENT

#### BY SUZANNE DEFFREE, MANAGING EDITOR, ONLINE

#### Engineering the next generation

he US Department of Commerce in July released a report on STEM (science/technology/engineering/mathematics) employment that stated some interesting facts (**Reference** 1). For example, the department projects that STEM occupations will grow by 17% from 2008 to 2018, compared with 9.8% growth for non-STEM occupations. STEM workers also command higher wages, earning 26% more than their non-STEM counterparts, and STEM-degree holders enjoy higher earnings, regardless of whether they work in STEM or non-STEM occupations.

All of these points are valuable when it comes to US competitiveness, individual earning power, and maintaining employment in what has in recent years proved to be a less-than-reliable career environment. It was the last point, however, that made me take notice of this report. Based on that point, *EDN* ran a blog post in August that started some good conversations on how to encourage kids toward STEM study and on the next generation of engineers.

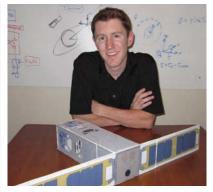

One of those conversations was with Aaron Goldstein (**photo**), an Arizona State University senior. Some lucky company will surely snatch him up when he receives his bachelor's degree next May. Goldstein's story starts like that of many other engineers: He played with Legos as a child, he liked to tinker, and he had a dad who sparked a curiosity in him to ask "why" and supported him along his way to a STEM education. His father even pointed out the blog post to him.

Goldstein is growing up to be a leader. In addition to interning with the National Aeronautics and Space Administration and aerospace companies, he rallied his fellow classmates and professors to start ASU's Sun Devil Satellite Laboratory. Through this group,

he and a handful of fellow ambitious students started out to build a functioning satellite. They have contacted NASA and are now waiting for a launch date, with expectations for early 2013.

Goldstein spent his college years on real-world projects and gained realworld experience while networking with real engineers, not simply practicing theory and academics. He speaks highly of his school but recognizes that what is taught at many universities is not engineering; it is science and mathematics on paper. Real-world application of a STEM education and what it means to be an engineer once that degree is in hand are more valuable than the degree itself in many ways, and the only way to get that experience is by working with other more experienced engineers.

Note that the headline on this editorial is not "Engineering: the next generation," which with the colon would grammatically mean that we were discussing the incoming work force of young, lessexperienced engineers. The headline, instead, uses "engineering" as a verb. We have to build the next generation of STEM professionals. These are the people who will one day sit where you sit, face the design challenges that you face, and innovate in ways and fields that we may not even imagine yet—but they won't get there without your help.

Understanding that, *EDN* and its sister publications will be hosting a meeting at ESC (Embedded Systems Conference) Boston in late September. We're looking for the slide-rule crowd of experienced engineers who would like to connect with the next generation, spending an hour or so offering real-world experiences and histories. Perhaps you'll choose to work for the long term with these kids—maybe become a mentor to some of them; that's up to you.

If you are new to engineering, so new that you've never touched a slide rule, we welcome you to come and pick the brains of those who have. There's a lot of knowledge for engineers to pass on from decades of hands-on work that you won't get in a textbook.

This networking event will be the first of many efforts we will make to help engineer the next generation. You'll find details on the meeting in the original STEM salary blog that started this project (http://bit.ly/STEM\_EDN). Also, be sure to sign up for ESC, the East Coast's leading embedded-systems event (http:// bit.ly/ESC\_EDN). Connect with your peers and spend a few minutes engineering the next generation.EDN

#### REFERENCE

Langdon, David; George McKittrick; David Beede; Beethika Khan; and Mark Doms, "STEM: Good Jobs Now and for the Future," US Department of Commerce, Economics and Statistics Administration, July 2011, http://bit.ly/ojvdjE.

Contact me at suzanne.deffree@ubm.com.

#### Our team will make the difference for your business.

With 42 years of success behind us, we're building upon our proven experience to implement new ways of doing business and introducing unprecedented strategies for hitting your goals. We are injecting a new level of commitment and an elevated sense of urgency to perform better than ever for your business today.

Call us today and experience the difference.

www.FutureElectronics.com

1-800-FUTURE-1

Integral ground/power plane rated up to 9.5 amps.

Q Strip<sup>®</sup> - The industry standard for low profile board stacking on 0,5mm, 0,635mm and 0,8mm pitch.

Q Rate<sup>®</sup> - Smaller footprints and lower profile right angle without sacrificing performance.

Q2<sup>™</sup> - Rugged contact system provides increased contact wipe.

Elevated, right angle, edge mount, power and shielding options.

Non Concerning of the Concerning of the

ининининини

ASSOCIATE PUBLISHER. **EDN WORLDWIDE** Bob Dumas, 1-516-562-5742; bob.dumas@ubm.com

DIRECTOR OF CONTENT, EDN AND DESIGNLINES Patrick Mannion 1-631-543-0445; patrick.mannion@ubm.com

EDITOR-AT-LARGE Ron Wilson EDA Tools, Chip Design, Services, Silicon 1-415-947-6317 ron.wilson@ubm.com

MANAGING EDITOR Amy Norcross Contributed technical articles 1-781-869-7971; amy.norcross@ubm.com

MANAGING EDITOR, ONLINE Suzanne Deffree Electronic Business. Distribution 1-631-266-3433; suzanne.deffree@ubm.com

TECHNICAL EDITOR Margery Conner Power Sources, Components, Green Engineering 1-805-461-8242; margery.conner@ubm.com

> **TECHNICAL EDITOR** Paul Rako Design Ideas, Analog, RF, PCB Design 1-408-745-1994; paul.rako@ubm.com

SENIOR ASSOCIATE EDITOR Frances T Granville. 1-781-869-7969: frances.granville@ubm.com

ASSOCIATE EDITOR Jessica MacNeil 1-781-869-7983; iessica.macneil@ubm.com

COLUMNISTS Howard Johnson, PhD, Signal Consulting Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap Kevin C Craig, PhD, Marquette University

UBM Electronics **CONTRIBUTING TECHNICAL EDITORS**

Dan Strassberg, strassbergedn@att.net Stephen Taranovich, staranovich@yahoo.com Nicholas Cravotta, editor@nicholascravotta.com Robert Cravotta, robert.cravotta@embeddedinsights.com

VICE PRESIDENT/DESIGN DIRECTOR Gene Fedele

> CREATIVE DIRECTOR David Nicastro

> > ART DIRECTOR Giulia Fini-Gulotta

PRODUCTION Adeline Cannone, Production Manager Laura Alvino, Production Artist Yoshihide Hohokabe, Production Artist Diane Malone, Production Artist

EDN EUROPE Graham Prophet, Editor, Reed Publishing gprophet@reedbusiness.fr

> EDN ASIA Grace Wu, Associate Publisher grace.wu@ednasia.com Vivek Nanda, Executive Editor vnanda@globalsources.com

EDN CHINA William Zhang, Publisher and Editorial Director william.zhang@ubm.com Jeff Lu, Executive Editor jeff.lu@ubm.com

ΕDN JΔΡΔΝ Masaya Ishida, Publisher mishida@mx.itmedia.co.jp Makoto Nishisaka, Editor mnishisa@mx.itmedia.co.jp

UBM ELECTRONICS MANAGEMENT TEAM Paul Miller, Chief Executive Officer, UBM Electronics and UBM Canon (Publishing) Brent Pearson, Chief Information Officer David Blaza, Senior Vice President Karen Field. Senior Vice President, Content Jean-Marie Enjuto, Vice President, Finance Barbara Couchois, Vice President, Partner Services and Operations Felicia Hamerman, Vice President, Marketing Amandeep Sandhu, Director of Audience Engagement and Analytics

For a complete list of editorial contacts, see http://ubmelectronics.com/editorial-contacts

Maximum products. Maximum inventory. Maximum value.

www.mill-max.com/EDN621

Over 800 styles in stock and more options

than any manufacturer in North America

**Available in diameters**

from .008" (.20mm) to .250" (6.35mm)

Receptacles feature a 4 or 6 finger beryllium copper

contact to ensure integrity of connection

Suitable for applications subject to high amounts of

vibration and shock or for use in harsh environments

Don't see what you need?

Rapid prototyping and custom designs are our specialty.

Follow us

MillMaxMfg I Mill-Max Mfg. Corp.

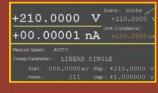

### Choose a bench-top SMU that's clearly more efficient.

| +210.0000 | v  | مبر Source: Voira<br>+210.0000 V   |

|-----------|----|------------------------------------|

| +00.00001 | nA | Lmit (Complance) :<br>+100.0000 µA |

| +10.50000 | A  | SOURCE: AMER<br>00.0000 A          |

| +06.00000 | v  | Unit (Concilance) :<br>+06.00000 v |

|           |    |                                    |

The superior GUI on the new Agilent bench-top source measurement unit (SMU) is the first in the industry to display your measurement results graphically. It also provides best-in-class output range and source/measurement resolution. For the testing speed and efficiency you need to deliver smart technologies to market faster, the choice is clear.

That's thinking ahead. That's Agilent.

| Agilent B2900A Series<br>Precision SMU |                                         |  |  |  |  |  |  |

|----------------------------------------|-----------------------------------------|--|--|--|--|--|--|

| Max output<br>range                    | 210 V, 3.03 A (DC) /<br>10.5 A (Pulsed) |  |  |  |  |  |  |

| Min resolution                         | 10 fA /<br>100 nV                       |  |  |  |  |  |  |

| Front panel GUI                        | 4 viewing modes on 4.3" color LCD       |  |  |  |  |  |  |

| $\wedge$  | 1            |                       |           |           |

|-----------|--------------|-----------------------|-----------|-----------|

|           | $\checkmark$ |                       |           |           |

|           |              | 1                     |           |           |

| $\bigvee$ |              | /                     | 1         | /         |

| 000.000 m | 41 +010.0    | 00 <b>11A 41 -</b> 0. | LO. DOOMA | 002.000 # |

© 2011 Agilent Technologies, Inc.

Learn how to make more efficient measurements by viewing a demo video or downloading application notes at: www.agilent.com/find/AgilentSMU

u.s. 1-800-829-4444 canada 1-877-894-4414

#### **Agilent Technologies**

# INNOVATIONS & INNOVATIONS

### Scope, spectrum-analyzer combination provides time-correlated signals

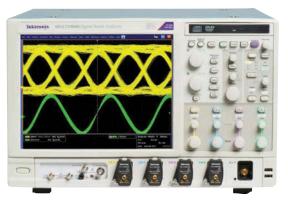

o address its belief that more than 60% of oscilloscope users also use a spectrum analyzer to troubleshoot embedded-system designs with integrated wireless functionality, Tektronix Inc has developed the MDO (mixed-domain oscilloscope). The MDO4000 enables work in both the time and the frequency domain to capture time-correlated analog, digital, and RF signals for a complete system view.

With the MDO4000, the RF-input frequency range extends to 6 GHz and provides a capture bandwidth of ≥1 GHz at all center frequencies, 100 times wider than that of typical spectrum analyzers. Users can see up to four decoded serial buses, parallel buses, or both at one time on the same display. The time correlation between domains enables accurate timing measurements for understanding delays and latencies between command and control events in a design and changes in the RF spectrum.

The MDO4000 also allows designers to view the RF spectrum of a signal at any time within a long acquisition to see how the spectrum changes over time or with device state. RF time-domain traces show how the amplitude, frequency, or phase of the RF input signal changes relative to time, which eases the characterization of frequency-hop transitions, settling times, and RF event timing relative to other system components and activities.

In addition to the standard RF power-level trigger, an optional module, MDO4TRIG, allows additional trigger types to use the RF power level as a source, enabling customers to further isolate an RF event of interest. Users can trigger on a specific pulse width, look for a time-out event or runt, or even include the RF

input in a logic pattern defined along with the analog and digital channels.

EDITED BY FRAN GRANVILLE

"It fundamentally changes what's involved in debugging designs with RF where there is a need to correlate events in the frequency domain with the time-domain phenomena that caused them," says Roy Siegel, general manager, oscilloscopes, at Tektronix. "Just as the MSO [mixed-signal oscilloscope] is the standard for embedded-design test, we expect the MDO will become the new standard for designs that increasingly include RF capabilities."

The MDO4000 enables debugging integration of common wireless modules below 6 GHz–WLAN, Bluetooth, and Zigbee, for example; debugging of common "homegrown" amplitude-, frequency-, or phase-modulated wireless communications; and wideband analysis of dual-band transceivers. US suggested list prices start at \$19,900. – by Colin Holland **Tektronix**, www.tek.com.

####

"Isn't it amazing how the folks in purchasing know so much more about parts than engineers know, and how they can improve a design by using cheaper parts?"

-Engineer William Ketel, in *EDN's* Talkback section, at http://bit. ly/qT1yrh. Add your comments.

The MDO4000 mixed-domain oscilloscope enables work in both the time and the frequency domain to capture timecorrelated analog, digital, and RF signals for a complete system view.

### pulse

#### Orca shows a full dual-mode Bluetooth core in CMOS

he market trajectory of Bluetooth shows the value of perseverance. From a premature launch resulting in something remarkably similar to abject failure, Bluetooth became the unquestioned standard for people who wanted to wear a lowgain microwave oven next to their skulls; recharge the thing every night; and frequently say, "Sorry, what was that?"

From such humble success, the standard has gone on to become a plausible \$75 replacement for a meter of six-conductor cable. And with the addition of the EDR (extended-data-rate) and lowenergy modes, Bluetooth could become, almost by default, a major factor in all sorts of nearfield communications, including the machine-to-machine kind.

As Bluetooth spreads into applications requiring significant levels of integration, it begins to present a problem for SOC (system-on-chip) designers. A Bluetooth transceiver is a relatively sophisticated 2.4-GHz spread-spectrum radio-not the sort of thing you license at RTL (register-transfer level) and hand off to a subcontractor to synthesize and integrate. Only a few complete Bluetooth-radio cores are on the market. Most of the IP (intellectual property) out there is in the form of building blocks for design teams who know their way around the inside of a digital radio.

This situation makes IP developer Orca Systems' recent announcement intriguing. The company has released a complete, turnkey Bluetooth radio—both the RF transceiver and the modem—supporting the original, EDR, and lowenergy modes. Supporting all three modes in a compact core necessarily means reusing most of the blocks in the signal paths.

That necessity in turn means that power management must exploit every opportunity the standard affords for clock gating; otherwise, the low-energy mode would consume about the same power as the original mode. Even so, the design may not be as energy-efficient as a low-energy-only core. For an SOC that must work in multiple modes, however, some savings are better than none.

The block is tiny: 2.7 mm<sup>2</sup> in Fujitsu's (www.fujitsu.com) 90-nm CMOS, including both the transceiver and the modem. Better yet, unlike most RF-CMOS designs that are nearly process-specific, it should scale well into finer geometries. Orca delivers the core as a single hard macro, including both transceiver and modem.

All of these features are possible, according to Joe Thome, Orca has so far produced the block in 130-, 90-, and 65-nm geometries, and it has scaled as predicted.

Orca's vice president for business development, because of the digital-radio technology that makes up Orca's crown jewels. The company's foundation is a digital open-loop frequency synthesizer that provides sufficient spectral purity for a Bluetooth transmitter but with low frequency-shift latency because of the open-loop architecture. Basically, it doesn't have to search and lock the way a PLL (phase-locked loop) does; it simply generates whatever frequency you program it to generate.

Orca designers directly modulate the synthesizer at the Bluetooth 1600-Hz hop rate, providing a fully digital signal source. Going a step further, Orca has developed a digital power amplifier to drive the antenna. This move is not unprecedented: Class D amplifiers at 2.4 GHz have appeared in the literature, notably from the University of California— Berkeley (www.berkeley.edu) at the 2008 Custom Integrated Circuits Conference. But it is hard to find any reference to a similar commercial product.

The designers did not stop there. Orca has also developed a mostly digital receiver chain. The design starts with a conventional analog low-noise amplifier, but, instead of analog filtering and mixing, the Orca design directly samples the RF, turning the continuous-time radio signal into a very-high-frequency sampled-data stream. The core does the filtering and mixing functions in the sampled-data domain, apparently somehow using digital circuitry to do so, and then passes the output to an ADC for use by the baseband processor.

These approaches provide several advantages for SOC designers, Thome says. The first is the size of the core. Without large matched RF transistors and passive components, the design is small. It is also scalable. The low-noise amp is a true analog device; otherwise, however, the radio area should scale almost like a purely digital block. Orca has so far produced the block in 130-, 90-, and 65-nm geometries, and it has scaled as predicted, Thome adds.

The DSP-RF architecture uses fewer inductors than would a conventional design. All of this digital talk suggests a standard digital process. A white paper from Fujitsu, which appears to describe the development of Orca's sample chip, says that the team used Fujitsu's 90-nm, low-power RF CMOS, with a special RF process-design kit. The core, the prototype IC, and an evaluation board are now available.

#### −by Ron Wilson ⊳Orca Systems,

www.orcasystems.com.

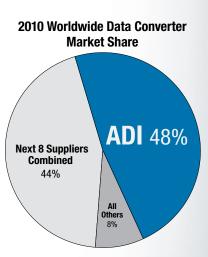

#### More engineers choose ADI data converters over the next 8 suppliers combined.

#### More products. More performance. More design support. More education.

With so many complex design problems relying on data converters to define system performance, and so many data converter suppliers to choose from, you might think it's remarkable that so many engineers agree on their choice: Analog Devices. As the world's #1 data converter supplier, ADI is your source for 1500+ converter products, all thoroughly and conservatively specified, and backed with more tools, training, and design support than any other supplier—by far. See why more engineers turn to ADI for answers to their toughest challenges. Explore products, customer stories, and design resources at *www.analog.com/ConverterLeader*.

#### **Leading Converter Innovations**

- AD9467: 16-Bit, 250 MSPS, IF Sampling ADC Provides outstanding SFDR performance over wide bandwidths; multiple on-chip functions and adjustability features for ease of use.

- ➤ AD5624R: Quad, 12-Bit SPI nanoDAC<sup>®</sup> Offers 12-bit accuracy (1 LSB INL) and on-chip 1.25 V or 2.5 V 5 ppm/°C reference, all in a 10-lead MSOP and 3 mm × 3 mm 10-lead LFCSP.

- AD7626: 16-Bit, 10 MSPS PulSAR® ADC Delivers an unequaled combination of effective resolution and speed, without compromising ac or dc performance, while reducing size and power.

#### AD9122: Dual, 16-bit, 1200 MSPS, TxDAC+® Transmit DAC

Enables multicarrier generation up to the Nyquist frequency and includes features optimized for direct conversion transmit applications.

Source: Databeans, Inc

#### **Circuits** from the **Lab** Beference Circuits

Lower your design risk and speed time to market with ADI lab tested reference circuits. Use a QR reader on your smartphone to watch video.

### pulse

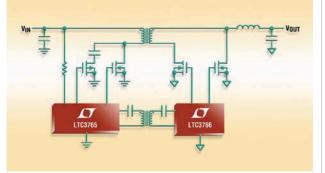

#### Synchronous, forward-converter chip set provides active clamp, deters transformer saturation

any dc/dc converters use transformers for isolation, potentially causing a problem: Following large, sudden changes in output load or input voltage, the loop closure may be too slow to prevent transformer saturation and resultant converter failure. To overcome this problem, Linear Technology Corp has introduced a pair of ICs that together implement a synchronous, forward-converter function with active-clamp reset and a flux-limiting capability to prevent such saturation under all conditions.

The direct-flux-limit LTC3765 primary-side intelligent IC works with the companion LTC3766 to create a self-starting, isolated, forward-converter topology. This type of forwardconverter design suits use in 12, 24, and 48V nominal-input

The LTC3765 and LTC3766 ICs together implement a synchronous, forward-converter function with active-clamp reset and a flux-limiting capability to prevent saturation under all conditions.

voltages that are common in telecom, data communications, and industrial applications.

After start-up, the LTC3765 receives timing signals and bias power from the secondary-side LTC3766 controller through a tiny pulse transformer. Secondary-side control puts the intelligence close to the load,

ensuring reliable control of the output voltage and current, providing fast transient response and eliminating the need for an optocoupler for isolation.

The LTC3765/LTC3766 contains control circuitry to implement an active-clamp transformer-reset technique, enabling efficiencies as high as 96% and greater power densities than those of conventional catch-winding or resonant-reset techniques. The design allows for adjustable delays for the high-current gate drivers for the main switch, the active-clamp switch, and the synchronous switches to achieve maximum efficiency. Other features include a fast and accurate average-current limit, fixed-frequency adjustable operation from 75 to 500 kHz, clean start-up into prebiased loads, multiphase operation for high-power designs, overtemperature protection, and true remote-output-voltage sense.

The LTC3765 is available in a thermally enhanced MSOP-16 package, and prices start at \$1.55 (1000). The LTC3766 is available in 4×5-mm QFN-28 and SSOP-28 packages, and prices start at \$2.60 (1000).

-by Bill Schweber Linear Technology Corp, www.linear.com/ product/LTC3765 and www.linear.com/product/ LTC3766.

The EpiCrystals true-

green laser module has

a bright, true-green color.

### True-green laser module targets use in smartphone picoprojectors

innish start-up EpiCrystals Inc has announced what it claims is the smallest and most efficient greenlight source for picoprojectors. EpiCrystals hopes that RGB (red/green/blue) laser technology will revolutionize smartphones, enabling them to project photos, video presentations, and movies on almost any surface with high-definition-level quality and resolution.

The EpiCrystals device uses frequency doubling to emit green light. According to Tomi Jouhti, vice president of business development, the laser comprises a GaAs (gallium-arsenide)-based, 1064-nm infrared laser chip and a PPLN (periodically poled lithium-nibate)-waveguide-type nonlinear crystal. The chip integrates a 45° folding mirror and lens, which the company The laser has a spectrum width of 0.5 to 1 nm to reduce speckle, more than 60 mW of optical output power, and greaterthan-100-MHz modulation speed.

builds at the wafer level, for efficient coupling. The emitted light is a bright, 532-nm color, which falls in the "true-green" spectral range of 515 to 535 nm.

The laser operates in passively Q-switched mode using simple construc-

tion and a three-contact laser and uses wideband QPM (guasiphase matching) and wideband SBG (surface Bragg grating) in the crystal, which locks the central frequency of the infrared laser. The laser also has a spectrum width of 0.5 to 1 nm to reduce speckle, has more than 60 mW of optical output power, and offers greater-than-100-MHz modulation speed. The TO56 module has a volume of approximately 0.2 cc and is compatible with MEMS (microelectromechanical-system), LCOS (liquid-crystal-onsilicon), and DLP (digital-light-processing) equipment. The green-laser module will be available in the first guarter of next year for \$45 (10,000).

– by Margery Conner >EpiCrystals, www.epicrystals.com.

### 100+ NEW CLOCK GENERATORS AND BUFFERS

#### LOW POWER, SMALL FOOTPRINT DEVICES FOR COST-SENSITIVE APPLICATIONS

Silicon Labs' broad portfolio of industry-leading clock generators, XOs, VCXOs, jitter attenuating clocks and clock buffers sets a new standard for flexibility, performance and lead times.

- Most frequency flexible timing solutions in the industry; ideal for multirate applications

- Available in industry-standard, drop-in compatible packages

- Based on patented DSPLL® and MultiSynth technologies, these low jitter products improve system performance, reduce BOM, minimize board space and simplify system design

- Helps reduce electromagnetic interference (EMI) and radio frequency interference (RFI) with a wide range of signal integrity adjustments such as rise/fall times, output impedance, drive strength and spread spectrum clocking

- All custom devices are available without NRE fees in <2-week lead times

| PRODUCT LINE                 | WIRELESS<br>INFRA-<br>STRUCTURE | OTN | соммѕ | BROADCAST<br>VIDEO | EMBEDDED | SERVERS | CONSUMER |

|------------------------------|---------------------------------|-----|-------|--------------------|----------|---------|----------|

| Jitter Attenuating<br>Clocks | •                               | ٠   | •     | •                  |          |         |          |

| Differential Clocks          | •                               | •   | •     | •                  | •        | •       |          |

| LVCMOS Clocks                |                                 |     | •     |                    | •        | •       | •        |

| PCI Express Clocks           |                                 |     | •     | •                  | •        | •       | •        |

| x86 Embedded<br>Clocks       |                                 |     | •     |                    | •        | •       | •        |

| Clock Buffers                | •                               | •   | •     | •                  | •        | •       |          |

| Oscillators                  | •                               | •   | •     | •                  | •        | •       | •        |

#### DIFFERENTIAL CLOCK GENERATORS

- Generates any frequency on any output up to 710 MHz with low phase jitter (<1 ps RMS)

- Any format on any output: LVPECL, LVDS, HCSL, CMOS, HSTL, SSTL

#### LVCMOS CLOCK GENERATORS

- Factory customized and I<sup>2</sup>C programmable

- Generates multiple frequencies with equivalent frequency synthesis capability of up to 8 PLLs

#### PCI EXPRESS GEN 1/2/3 CLOCKS

- Up to 9 HCSL and up to 6 LVCMOS outputs

- Fully integrated terminator resistors on each output

- 35% lower power than competing solutions

#### EMBEDDED x86 CLOCKS

• Extensive family of Intel-compliant x86 clocks for embedded computing, communications, enterprise & industrial applications

#### **EMI REDUCTION CLOCKS**

- Spread percent from 0 to 5.0%

- Down or center spread options

- Spread modulation frequency 16 128 kHz

#### FANOUT & ZERO DELAY CLOCK BUFFERS

• Low power (2.7 mA typ), small size 10-TDFN (1.4 mm x 2.0 mm x 0.75 mm), very low phase noise (-168 dBc @ 1 MHz)

#### Find the perfect part for your application at www.silabs.com/parametric-search

©2011 Silicon Laboratories Inc. All rights reserved. \*Requires QR code reader; download at reader.kaywa.com. Data charges may apply.

### pulse

### Bridgelux plans to bring economies of GaN-on-Si to HB LEDs in 24 months

ridgelux Inc recently announced its success in demonstrating GaN (gallium-nitride)-on-Si (silicon)-wafer LEDs with performance levels comparable to state-of-the-art GaN-onsapphire or GaN-on-SiC (silicon-carbide)-based HB (highbrightness) LEDs. Cool-white LEDs show efficiencies as high as 160 lumens/W at a CCT (correlated color temperature) of 4350K, and warm-white LEDs deliver 125 lumens/W at a color temperature of 2940K and a CRI (color-rendering index) of 80. These numbers represent results of lab demonstrations at pulsed currents. The company claims that the lumen-per-watt values are the highest yet for GaN-on-Si LEDs.

Basing LEDs on less-expensive 8-in. silicon wafers will enable significant price drops in LEDs that will ultimately ripple through to the price of

LED-based light bulbs. A thermal mismatch between GaN and Si can cause the epitaxial

Bridgelux has demonstrated GaN-on-Si HB LEDs with performance comparable with that of LEDs employing SiC or ionsapphire wafers, an advance that can ultimately result in lowerpriced LED bulbs. films to crack or the wafers to bow during or after manufacturing. The company claims, however, that its proprietary buffer-layer process produces crack-free, flat wafers. Bridgelux plans to deliver GaN-on-Si devices to the commercial market within 24 months.

"Roughly speaking, LED chips [the emitter itself, unpackaged] cost about 25 cents/chip," says Brad Bullington, vice president of strategy at Bridgelux. "Over the next 24 months, ... this technology will give us a path to sub 10 cents on launch [in 2013] and the mid- to low single digits thereafter." Bullington adds that the major barrier to adoption of LED lighting is its upfront cost and that this technology move will bring \$5 billion to \$7 billion in additional revenue to LED lighting in the 2013 to 2015 time frame.

—by Margery Conner ▷Bridgelux, www.bridgelux.com.

#### Watch out for well-made – but counterfeit – chips

An eye-opening blog post reveals logic-analyzer developer Saleae's experience with counterfeit parts (Reference 1). Saleae co-founder Joe Garrison first became aware that his company had a problem with counterfeits when an unusually large number of boards started failing the functional test. Garrison noticed that the USB (Universal Serial Bus) chip was running hot—not just on the failures but also on the good boards. Because the company uses Asia as a source for these boards, Garrison immediately wondered whether they were counterfeits. Aren't counterfeit parts always duds, though?

"There was little or no information online about this part, but I did uncover some random snippet that said the part was flagged for possible counterfeit activity just two months prior—not a good sign," Garrison says.

Searching further, he learned that a huge number of counterfeit parts are so-called reclaimed parts. To "reclaim" these parts, counterfeiters strip discarded electronics of any high-value components and then resell them as new in fake packaging. This process involves cleaning and relabeling the parts—in some cases with new part or batch numbers. "Apparently, this [behavior] is a staggeringly large illicit business," Garrison explains (Reference 2).

The parts may be from similar functional parts or may be different. Saleae verifies that the USB chip was a reclaimed instance of an ancient version of a part. The report also says that nonfranchised distributors are supplying almost all of the parts. Buyer <u>beware. – by Margery Conner</u>

Saleae, www.saleae.com.

#### REFERENCES

<sup>1</sup> Garrison, Joe, "Counterfeit parts are a big headache," Joe Garrison 2011 Web Edition, Aug 11, 2011, http://bit.ly/pw32HE.

<sup>2</sup> Hughitt, Brian, "Counterfeit Electronic Parts," Trilateral Safety and Mission Assurance

Conference, National Aeronautics and Space Administration/European Space Agency/ Japan Aerospace Exploration Agency, April 2008, http://1.usa.gov/nDQSCo.

New! IGBT reference book Order now under www.infineon.com/igbt-book

#### Solutions for windpower systems Energy-efficient components for high system reliability

The Infineon product portfolio provides components for the highest energy efficiency in windmill power converter and pitch control solutions.

000

Our Power Modules with newest 1200V/1700V trench fieldstop IGBT4 and Emitter Controlled diode chip technology offer best in class power density solutions in conjunction with extended lifetime. The modules feature low on state losses, optimized soft switching behavior and a wide operation temperature range up to 150°C maximum junction operation temperature. The newly introduced stack assembly ModSTACK<sup>™</sup> HD leads to more than 50 % higher power density at same footprint.

#### The following benefits are provided to our customers:

- Extended module utilization by 150°C maximum junction operation temperature

- Highest power density

- Supreme power cycling and thermal cycling capability

www.infineon.com/highpower

### pulse

#### New architecture promises better battery

A change in architecture is promising to close the gap between semiconductor technology and battery technology, which has traditionally lagged behind semiconductors due to its dependence on unchangeable chemical reactions. Instead of storing charge in a main battery—then doling it out to individual devices on demand—a new breed of hybrid capacitor/battery is storing just enough energy for an adjacent device for its exclusive use. Ioxus Inc claims to be solving the battery problem by defining a new distributed-energy architecture.

Users are employing the company's hybrid ultracapacitors for all types of applications that were challenging for traditional battery architectures, according to Chad Hall, co-founder and vice president of loxus. The device satisfies the needs of short-term or backup power, without the problems of traditional batteries, he claims.

Applications for the technology range from simple to complex. For instance, it allows users to charge a simple flashlight in just 20 seconds using a hybrid ultracapacitor; the flashlight can then continue to operate for as long as two hours, according to Hall. A complex regenerative-braking system on an automobile can instead use a hybrid ultracapacitor that charges whenever you brake and stop. It then simply restarts the car when you hit the gas pedal—eliminating all the pollution that stop-and-start traffic causes. to economically distribute hybrid capacitors around a vehicle, storing shortterm energy as necessary for powering LEDs, onboard computers, power windows, power door locks, and security systems. In the event of a total failure—or even removal—of the main car battery, all hybrid-ultracapacitor-powered systems still work. Ioxus estimates that electric vehicles using distributed hybrid ultracapacitors rather than a centralized battery can cut 20 to 30 lbs from their weight.

A few other manufacturers claim to have developed similar hybrid ultracapacitors. For instance, Evans Capacitor Co (www.evanscap.com) has a highervoltage, lower-energy hybrid capacitor, but it is more akin to an ultracapacitor alone than loxus' hybrid ultracapacitors. And JM Energy Corp (www.jmenergy.co.jp) offers a lithium-ion capacitor that is more like a lithium-ion battery than loxus' hybrid ultracapacitor. loxus claims to have intellectual property that makes its approach better than Evans' and safer than JM Energy's.

The ultracapacitors combine the architecture of a capacitor—charge accumulating on plates separated by an insulator with the chemical storage of a lithium-ion battery. Using the same chemistry as a lithium-ion battery, the device distributes those chemicals onto the surface of a solid electrode, rather than embedding them into a porous electrode, requiring the slow process of intercalation to charge and discharge them. POWER (W) BATTERY ULTRACAPACITOR ENERGY (WHR)

loxus hybrid ultracapacitors with built-in lithium-ion batteries enable distributed storage architectures that work better than either technology alone.

charge the devices at nearly any rate, allowing them to absorb and discharge vast or minuscule currents, depending on an application's requirements. However, they can neither store as much charge volume nor store it for as long as a traditional battery, but the applications' distributed architecture compensates for these shortcomings, according to loxus.

Hybrid ultracapacitors store less charge than do lithium-ion batteries, but they store about 100% more charge than an ultracapacitor alone and provide almost unlimited charge/discharge cycling. You can charge and discharge most lithium-ion batteries only a few hundred times, and even special long-term versions have only a few thousand cycles. You can charge and discharge hybrid ultracapacitors, on the other hand, more times than the lifetime of the product in which you are using them more than 20,000 cycles in loxus tests.

Automotive applications allow designers

As a result, users can charge and dis-

−by R Colin Johnson ⊳loxus, www.ioxus.com.

#### Source code for $\mu$ C/OS-III is now available

$\begin{array}{c} & \text{icrium is making available for evaluation the source code of its latest real-time operating system, <math display="inline">\mu C/OS$ -III. The move comes as the private company claims it is seeing double-digit growth in sales and calls for evaluation boards using a variety of processors. Micrium in 2009 released its third-generation RTOS with a handful of evaluation boards and a book describing the software's \\ \end{array}

capabilities. The company in 1999 released the previous version of the RTOS, which is available as source code for evaluation.

The latest version of the book on  $\mu$ C/OS-III, now available as a free download, also includes a section with example code for four medical-electronics systems, including a pulse oximeter and a blood-glucose meter. The company aims to expand its efforts to

provide technical documentation for other vertical markets. Universities and researchers can freely download and use the company's RTOSs. Commercial users are subject to licensing fees.

Jean J Labrosse, founder and chief executive of Micrium, claims that the company is the only commercial RTOS provider that offers source code for evaluation use. OEMs that roll their own RTOS still represent the largest slice of the market, with those using free, open-source RTOSs coming in second, says Mike Phipps, director of sales, marketing, and business development for the company. However, Micrium has been gaining share since Intel (www.intel. com) purchased Wind River, Phipps claims.

-by Rick Merritt

**Micrium**, www.micrium.com.

### IP WAIVERS CAN BE A REAL DRAG.

**SET YOUR DESIGNERS FREE WITH CALIBRE® AUTOMATIC WAIVERS** | It keeps track of waivers and eliminates them from SoC verification results, saving hours of wasted effort by you and your ecosystem partners. Now your designers can do more productive things. Take a test drive at: http://go.mentor.com/autowaivers.

92011 Mentor Graphics Corporation. All Rights Reserved. Mentor Graphics is a registered trademark of Mentor Graphics Corporation.

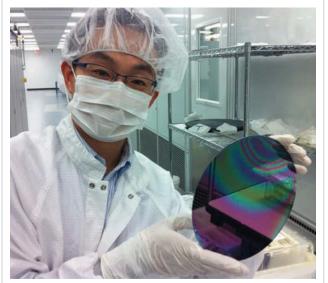

INSIDE NANOTECHNOLOGY

#### BY PALLAB CHATTERJEE, CONTRIBUTING TECHNICAL EDITOR

#### Semiconductors develop an EUV ecosystem

he need to drive to smaller geometries is not slowing down, despite the rising cost of building wafer fabs. Lithography has been a major element in this push toward new sub-20-nm process geometries. The shift from 193-nm, DUV (deep-ultraviolet) lithography to 11- to 14-nm, EUV (extreme-ultraviolet) lithography requires a full ecosystem for the materials and methods, along with an imaging module. The ecosystem includes a supply of masks, photoresist, and both mask- and wafer-metrology tools and methods.

The system works by inspecting blanks and associating defects with the "dark-field" patterns of the blanks. The geometry of the defects in question is incompatible with standard optical-inspection techniques. As a result, vendors are using AIMS (aerialimage-message-system), ABI (actinicblank-inspection), and advanced-PMI (patterned-mask-inspection) tools for defect review. In addition to using these inspection tools, manufacturers must create repair methods. For standard masks, the normal repair technique is to use a 30-kV FIB (focused-ion beam) to fix the patterns on the

mask. For EUV masks, due to the wavelength used, underlayer and multilayer damage can occur.

Several viable options are available to repair this damage. For example, manufacturers could use a 10-kV FIB, but this method has some selectivity and reflectance issues. They could also try nanomachining with a diamond tip. This method causes little substrate damage but results in a lot of debris and works only on certain patterns. Alternatively, they could attempt e-beam repair, which offers high selectivity but has issues with the high corrosiveness of the xenon difluoride, which clears the debris from the repair. Another major issue with repair and inspection is the throughput, which is currently a factor of 10 behind DUV approaches for similar tasks.

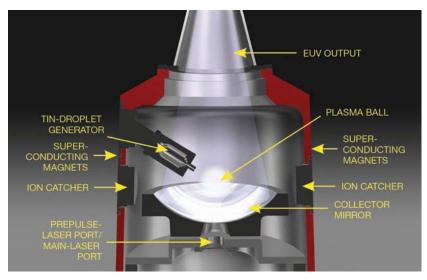

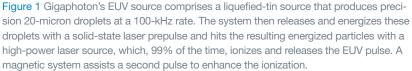

Manufacturers are making progress on the patterning side, however. Gigaphoton Inc (www.gigaphoton.com) now has a 100W EUV source that, in an imaging system, can support a throughput of 50 wafers per hour. The company is developing a 250W source that will support 150 wafers per hour. The EUV source comprises a liquefied-tin source that produces precision 20-micron droplets at a 100-kHz rate. The system then releases and energizes these droplets with a solid-state laser prepulse and hits the resulting energized particles with a high-power laser source, which, 99% of the time, ionizes and releases the EUV pulse. A magnetic system assists a second pulse to enhance the ionization (Figure 1). This environment yields a debris deposition rate of 1.2-nm/million pulses, and the chamber-cleaning rate is based on a debris accumulation of 4.4nm/million pulses.

Another issue is the protection of the masks. To protect them, manufacturers must use exotic techniques, such as a pattern of buffer/absorber/buffer and antireflective caps. Techniques for reticle management must extend to reticle shipping, particle management from the shipping pod, storage, and protection from ESD (electrostatic discharge). EDN

Pallab Chatterjee is on the IEEE Nanotechnology Council.

### { printf ("Hello World!\n");

#### Introducing ZYNQ, the new element in processing.

Finally, the processor comes together with the FPGA in a fully extensible processing platform called Zynq.<sup>™</sup> More intuitive to program in the way you already know. Fully customizable to your requirements. Faster to

implement and get to market. As a software engineer, if you know ARM<sup>®</sup> Cortex,<sup>™</sup> you already know Zynq. And if you know Xilinx, you already know this is innovation you can count on. **Visit us at www.xilinx.com**

© Copyright 2011. Xilinx, Inc. XILINX, the Xilinx logo, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners. ARM is the registered trademark of ARM Limited in the EU and other countries.

### We've just made reaching your goals easier than ever.

#### Finding the right solution to your company's materials' needs has never been easier, because now the companies of Brush Engineered Materials have unified under one name, Materion. It allows us to give you greater access to all of the resources and solutions we offer. So why not find out what the new Materion can do for you? Chances are, we can make a big difference to your technologies and your bottom line. Find out more at materion.com.

Before.

After.

ON

Brush Engineered Materials, Williams Advanced Materials, Brush Wellman, Academy Corporation, Barr Associates, CERAC, Technical Materials, Inc. Techni-Met, Thin Film Technologies, and CERAC are all now MATERION.

### CHIP-AND-PACKAGE CO-DESIGN RELIEVES PRESSURE ON COMPLEX DESIGNS

#### **BY DARVIN EDWARDS • TEXAS INSTRUMENTS**

he vise is closing down on design departments. Manufacturers want more capabilities in their products than ever before. It's imperative for manufacturers to remain competitive. Marketing, meanwhile, wants to cram that added performance into less space. Consider all of the handheld devices that are prevalent today. The pressure doesn't stop there, though.

Design cycles keep getting shorter and shorter. A long design cycle increases the risk that the manufacturer might miss a market opportunity, and doing so can be catastrophic. Design must do more, in less space and with less time. CO-DESIGN ACCOMPLISHES **MORE WITH LESS** BY PERFORMING MORE DESIGN TASKS IN A SHORTER DESIGN CYCLE.

fficiency

Enter co-design. Manufacturers should be constantly examining all aspects of design to verify that they are meeting all of the performance targets for final products. With each successive performance-target verification and finetuning, the overall value of the product to the user increases, and the risk of a failed product launch diminishes. The goal is to accomplish more with a shorter design cycle by concurrently executing more design tasks. Of course, one of the ultimate goals is that first prototypes will function to spec, avoiding the dreaded design re-spin. Failed products that require design re-spins are costly on many fronts for both semiconductor manufacturers and their customers.

Designers have for some time employed the notion of co-designor its predecessor concept, concurrent engineering. Managers assign teams portions of a design to execute in parallel with the rest of the design. What has changed is that co-design is now appearing in every aspect of a design project-from inception; to planning; to integration in the final system; and even to the use-profile assumptions, such as how long a user might play a game or use a smartphone. An area receiving increasing attention is chipand-package interaction, which analyzes characteristics of the package with the performance of the chip. Designers place more emphasis on chip-andpackage interaction as both chips and packages become more complex and as 3-D-packaging technologies more intimately link the interactions among package technologies and the architecture of the system in the package.

#### **CHIP/PACKAGE CO-DESIGN**

Chip-and-package co-design concurrently initiates package design with custom die and even system-level design. With this method, a team can quickly bring a new product to market and achieve the performance characteristics required to be competitive. In

#### Today's schedules require codesign of all facets of the system. Simulation and accurate modeling are vital to co-design efforts. An emerging subset of co-design is die/package/board co-design. Electrical, thermal, and mechanical issues are all important.

AT A GLANCE

addition to the normal challenges that revolve around optimizing the performance characteristics of the eventual device, certain foundational challenges are inherent in every chip-andpackage co-design effort. These challenges involve people working together and software tools that can share databases to quickly evaluate design characteristics.

At the beginning of a co-design project, all of the various design disciplines must come together. A chip-and-package co-design effort includes experts on all the elements in the silicon-production process, including transistor-design libraries, I/O (input/output) cells, packaging and materials, manufacturing and assembly, and chip test. Getting such a large group together may not involve a physical meeting of everyone on the team, but it must involve a merging of intentions for everyone. For the project to succeed, all of the key players from across all design areas must share the common goal of creating an optimized end product.

At the onset of the chip-and-package co-design project, representatives of each discipline must understand the chief needs of every other discipline. For example, the electrical-layout engineers must be aware of any thermal limitations in the package that could require a change in the placement of logic or I/O blocks to reduce operating temperatures. In addition, circuit designers must create any analog circuits that are sensitive to package-stress gradients with specific package limitations in mind.

Moreover, packages must supply the required number of I/Os for the chip layout, and manufacturability concerns may dictate specific rules so that the product meets the requirements of high-volume production. In the end, the team must be cognizant of the target cost of the product to avoid choosing too-expensive options. Some concerns of team members may evoke more passionate responses than others, but eventually the entire team must pull together around the common goal, which will come down to delivering a compelling and engaging experience for the end user of the product.

Management's commitment to the project's common goal and to co-design as part of achieving this goal is essential. Conflicts among groups and even individuals who make up the co-design team may occur. Management should encourage constructive debate with the objective of arriving at the most effective approach. The leaders of the effort must occasionally guide the direction of the team when it cannot reach unanimity among conflicting positions.

#### THE COMMON DENOMINATOR

One of the basic characteristics of every co-design project is the necessity for design teams to concurrently complete their work on a part of the overall design while other teams are developing other aspects of the design. For example, one team may be developing a chip layout while another team is selecting and designing a package construction.

Selection of system parameters, such as the PCB (printed-circuit-board) area

WITH EACH PERFORMANCE-TARGET VERIFICATION AND FINE-TUNING, THE VALUE OF THE PRODUCT TO THE USER INCREASES, AND THE RISK OF A FAILED PRODUCT LAUNCH DIMINISHES.

### Is your scope lying to you? Find out. Rohde-Schwarz-scopes.com

If you're not using a new Rohde & Schwarz digital oscilloscope, your scope may not be giving you honest answers.

Try the industry's most accurate and reliable digital oscilloscope.

888-837-8772 www.rohde-schwarz-scopes.com

that is available for a device, may drive packaging decisions and, in turn, affect die layout. Software simulations might sometimes identify significant power usage in a portion of the circuit, and these simulations could drive the need for thermal enhancements in the package. When tight schedules eliminate any chance of prototyping the design, designers must quickly simulate accurate component connections if the team wants to have multiple options.

Simulation tools generate a model of the chip and its package to analyze how various design options will affect the parametric performance of the device. For example, a simulated model of the device might analyze how a change in the package affects the electrical noise on the power-and-ground plane of the device or how a change in the package might alter the temperature on part of the device. Modeling the effects of packaging options on a device's I/Os is also critical. Not so many years ago, a complex device might involve only several hundred I/Os. Now, the number of I/Os on a complex SOC (system-on-chip) device could easily reach 2000 or 3000, all of which couple together. To end up with the best possible device, the modeling tool must be able to analyze how a change in a package-design parameter, such as a power plane, would electrically affect all of these I/Os.

This type of scenario can be daunting for software-simulation tools. During a co-design project, the speed and abilities of the tools environment are critical. The time window for considering various package innovations is usually narrow. A faster simulation tool produces more models over a shorter period, meaning that the design team can consider a greater

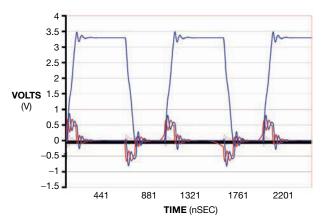

Figure 1 A typical electrical simulation of a signal injected into a package pin shows the distortion of the signal by the package "circuit" and the noise it induces on neighboring leads.

number of options to find the best approach. For example, if the software tools require a week to generate a complete model of the device and the team faces a schedule milestone three weeks away, the team can consider only relatively few alternatives without disrupting the project's overall time line.

In a perfect world, computational resources would not limit simulation. The team could characterize and understand the many interactions among the design parameters. Simulation would explore multiple routing options, material choices, reliability margins, cost minimizations, manufacturability studies, die-size minimizations, and power margins. Developmentsoftware systems would automatically adjust the chip, package, and system design until all parameters were optimal.

This scenario is the long-term dream for co-design. In reality, though, current software and hardware systems have limitations. As a result, designers use their expertise to input their best options. A finite number of simulations then point out the areas in which additional optimization may be necessary. Designers change the designs and validate the alterations.

#### MAKING THE MODEL

Engineers and technicians need time to describe a device, its package, and the system to the various analysis tools, slowing down modeling and affecting the effectiveness of a chip-and-package co-design project. To generate a simulated model of a device, the software tool must have a detailed description or a language-based model of the device. Changes to the device design should be simple to input because this approach eases optimization. Unfortunately, this scenario occurs infrequently.

Describing the device geometries and the package layout to one or more tools can be laborious and tedious. It is difficult to describe the 3-D world of a real chip, package, and system in the words of the computer-simulation tools. Designers must divide the 3-D geometry into many elements through "meshing." Mathematical functions, which relate elements to surrounding elements, describe the parameters for modeling, producing many simultaneous equations for the computer to solve. The accuracy of the solution is dependent on the quality of the subdivision of the 3-D solid and on how well the individual elements capture the gradients of the fields to be calculated. The physics of a device design could require different types of meshes. Some may need only surface meshes, whereas others require full 3-D representations.

In most instances, models must capture the interfaces of one material to another, sometimes requiring that the mesh be continuous across the boundaries of all components or structures in the design. For example, the mesh of a circuit trace must be continuous with the mesh of the surrounding substrate's polymer to calculate interfacial stresses. In addition, whenever someone makes a change to the design, designers must remesh it.

These tasks often prove too difficult for current software tools without significant human intervention guiding them and supplying knowledge to the software to identify the order the tool should take for meshing complex geometries. Because each area of physics involves different types of meshes, experts often must manually repeat this intensive process during various steps.

This type of human intervention adds little value to the design-optimization task. The software tools should use adaptive meshing to automate this repeated meshing and check the mesh against the physics of the problem to identify where mesh refinement is necessary and to generate an accurate result. Once adaptive meshing and other automation features become standard features of all analysis tools, the time to describe a device will become dramatically shorter.

#### **OPTIMIZED PACKAGING**

Time to market is one of the primary forces that drives chip-and-package codesign projects. After all, time is money, and you can never regain missed opportunities in the market. Another good reason for chip-and-package co-design is to achieve a product that excels in the market. Poorly optimized designs don't deliver the performance that users expect, often resulting in product recalls and loss of market share.

For example, a poorly optimized chip design might consume more power than the system can efficiently handle, necessitating more expensive cooling features. A design that uses less power for the same performance will achieve more market success in a portable-system application, in which battery life is a key consideration. Users prefer a smaller portable device with a low profile and small footprint over a larger device with the same features. Moreover, if one chip runs faster than another for the same performance and cost, the faster chip will likely win market share. In general, the chip-and-package co-design team will examine, analyze, and evaluate all of the electrical, thermal, and thermomechanical characteristics of a device and its package.

#### **ELECTRICAL ISSUES**

One of the first concerns of chip and package designers is which chip-interconnection technology to use. Flip-chip interconnection can still be more expensive than a wire-bonded approach. A wire-bonded package that is compatible

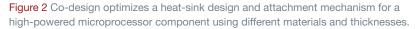

### Scope Lie #1 Your digital scope's bandwidth

When it comes to small signal bandwidth, engineers need a gradual signal roll-off to avoid seeing a lot of ringing and overshoot in the time domain.

Today's digital scopes employ very sharp, high-order frequency responses that trade minimum sampling rates for maximum bandwidth. The result is high overshoot and ringing when measuring typical digital signals.

Try the scope that tells the truth by utilizing slow roll off to eliminate overshoot and ringing.

Discover how your digital scope may be misrepresenting results at

www.rohde-schwarz-scopes.com

OHDE&SCHWARZ

888-837-8772

- 0.4 Watts to 50 Watts

- 115V/26V-400 Hz Primary

- Secondary Voltages 5V to 300V

- Manufactured to MIL-PRF 27 Grade 5, Class S, (Class V, 155°C available)

- Surface Mount or Plug-In

- Smallest possible size

**INDUSTRIAL · COTS · MILITARY**

with the device's I/O count, speed, and performance specifications can result in significant cost reductions over the lifetime of a device. To select the best alternative, teams do electrical analysis on those products whose performance requirements overlap the capabilities of wire-bond and flip-chip interconnections. The rest of the package design flows from this selection.

A primary concern is whether enough power is getting onto the device for it to function at its specified level. The device's package plays a major role in this regard because the resistance, inductance, and capacitance of the power and ground pins can distort the supply of clean power to the chip, creating power and ground bounce or noise. Chip-and-package co-designers simulate the electrical design of chips and packages with an eye toward analyzing the electrical noise on the power and ground pins and planes.

The simulation software can highlight areas of high noise, inductance, current density, or resistance for optimization. A redesign can then minimize the problems. A simulation sometimes indicates that filtering capacitance is necessary to reduce power and ground noise. These analyses should also consider the power- and ground-distribution planes in the system-level PCB, or at least apply a valid simplification of the system-level planes as a boundary condition.

Engineers should also devote much analysis to simulations of the electrical load on the device's I/Os. Timing and noise analysis will identify a poorly laid-out high-speed I/O on the substrate (Figure 1). For example, two single-ended lines that are too close together may induce coupling noise on both lines. Separating these lines or adding a ground between them might be necessary to reduce the signal coupling. In other instances, changing the current-return paths of an I/O to reduce or increase inductance might be necessary. Simulations can also explore manufacturability issues, such as tracewidth or substrate-thickness variations, and response versus frequency. The goal is to ensure that the package imparts the least distortion to the signal.

#### THERMAL CONSIDERATIONS

Every power-consuming device is also a small heater that requires a means of power dissipation. Often, when a component's power consumption exceeds 1W, the thermal needs of the chip drive the package choice. An effective chip-andpackage co-design team examines how to best design the device's package to conduct heat away from the device and toward the underlying PCB or to a heat sink, depending on the system application.

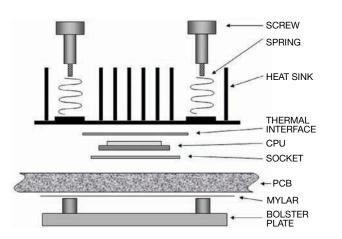

Co-design ensures that the package conducts heat where it needs to go, helping to minimize the temperature of hot spots on the die. With BGA (ballgrid-array) packages, for example, thermal vias can conduct heat away from the die and to the PCB. Some package configurations include heat sinks to efficiently conduct heat energy away from the die (Figure 2). All devices have maximum-temperature limits. Exceeding these limits causes the device to stop operating or causes damage to the device. Co-design plays a major role in ensuring that devices remain within their temperature limits.

#### STRESS

Thermomechanical-stress issues as they relate to chip-and-package co-design involve the mechanical interaction of the die, the package, and the system. These issues affect the reliability of not just the chip but also the end-use device. For example, DSPs for wireless base stations must be able to withstand swings from the high temperatures of a desert to the extreme cold of an Alaskan winter or a high mountaintop. These extreme conditions must not cause delamination of the various package layers or fatal fatigue of the solder balls that make the electrical connection to the PCB. The base station is only as reliable as the DSP chips that operate it, and the interaction between the chip and its package affects the DSP chips' reliability.

Thermomechanical analysis reveals whether the package's stress gradient is the best for the chip's parametric performance. This analysis is particularly important with analog chips because stress-related gradients across the device can create shifts in the parametric characteristics of the transistors or resistors, resulting in deviations in the linearity, gain, voltage offset, and other characteristics of the device.

A chip-package analysis of the mechanical robustness of a device might lead to the deployment of a different

material in the package or the inclusion of a structural element in the device. For example, process engineers work to implement new on-chip dielectrics in semiconductors because these materials reduce capacitance between the lines on a chip and enable higher switching speeds. These dielectrics are sometimes less dense and less structurally robust than other materials, however. The chip-and-package co-design team would need to simulate a new dielectric in the device to analyze whether the chip would be able to withstand a certain level of mechanical stress. Dangerously high levels of stress in the predictions might trigger a materials change or a new design rule to structurally strengthen the device.

Warping is another important concern for thermomechanical co-design engineers. Packages are laminates of multiple layers of different materials, each with its own expansion and stiffness. Passage through a temperature cycle can cause warping, which can in turn cause the package's leads or solder balls either to not contact the PCB during soldering or to put too much pressure on the joint, which could result in solder bridging. Thermomechanical analysis can predict this warping and point out the need for different materials or structures if the warping is too severe. Shadow moiré, a measurement tool, further characterizes the warping and validates the thermomechanical modeling.

#### **CALIBRATION AND VALIDATION**

In many regards, chip-and-package codesign depends on modeling and other tools to simulate either portions of a design or the entire device so that the design team can study the effects of various design options, eventually resulting in a fully optimized design. The outcome of a chip-and-package co-design effort will be successful only if the tool's outputs are accurate. A tool that returns an inaccurate result can wreak more havoc on a chip-and-package co-design project than having no result at all. The design team could take the wrong path by using faulty simulation information and not realize the mistake until the project has progressed significantly along its time lines. The team can never recoup the wasted time.

Because of these issues, experienced co-design teams constantly calibrate and validate the tools that are essential to the process. The most fundamental way of completing this task is to analyze the characteristics of devices both before and after manufacturing. Any discrepancy indicates a tool in need of recalibration.